|

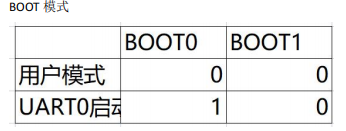

AG32/AGRV2K硬件设计注意事项AG32/AGRV2K硬件设计注意事项: 1、HSE外部晶体的范围4~16MHz,推荐8MHz。 2、VDD/VDDA的范围都是3.15~3.45V,CPLD对电源纹波的要求相对较高。 3、.除了ADC,DAC,CMP,USB,OSC,JTAG,这些端口不能重新映射,其它数字部分端口都可以重新映射到带IO的PIN上。 4、芯片支持SWD下载,使用SWDCLK(TCK),SWDIO(TMS),GND即可。 5、串口下载只支持UARTO,不能重新映射。串口下载时,注意BOOT0(高),BOOT1(低)。 6、为了更好通过EFT测试。VDDA前面加上磁珠。这部分是给PLL,ADC等供电的。VDD33前最好也能加磁珠。 7、BOOT0建议不要直接接地,而通过电阻接地。调试时,如果烧录了错误程序而导致系统异常的话,可能无法再此下载程序。此时,需要将boot0拉高上电,这样不会再运行用户程序,这样就可以重新下载。 8、MCU+CPLD应用时,如果要用有源晶振,时钟从OSC_IN引入。如果时纯CPLD应用有源时钟请从带IO_GB的PIN引入。 9、上电引脚电平:

注意,其它I0上电时是floating状态。需要等logic部分配置生效后,用户配置的10上下拉才能生效。这个配置时间与logic部分是否压缩及文件大小本身有关,一般在20~40mS左右。如果用户对硬件电路上的上电电平有要求的话,尽量使用外加电阻实现上下拉。内部上下拉电阻的阻值大小一般在40k左右。

JTAG IO JTAG PIN 也可以复用成 IO。但是这些 PIN 默认是 JTAG 功能,因此当作普通 IO 使用 前,必须先 disable。 比如 SYS_DisableNJTRST()、SYS_DisableJTDI()、SYS_DisableJTDO()。 需要获取更多的“资料”和“支持”和“样片测样申请”可以联系我们 提供“芯片测样-发送资料-技术支持-批量采购” 联系方式: 姚工 13661545024(VX同号) (加的时候备注下公司名和个人名字) 在线商城:agm-micro.taobao.com 公司网站:www.agm-micro.com 资料网站: www.tcx-micro.com |